您现在的位置是:首页 > 电路图 > 电路图学习 > 电路图学习

FPGA开发配置模式电路设计精华集锦

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-08-18

简介FPGA共有四种配置模式:从串模式(Slave Serial),主串模式(Master Serial),从并模式(Slave Parallel/SelectMap)以及边界扫描模式(Boundary-Scan)。具体的配置模式由模式选择引脚M2﹑M1﹑M0决

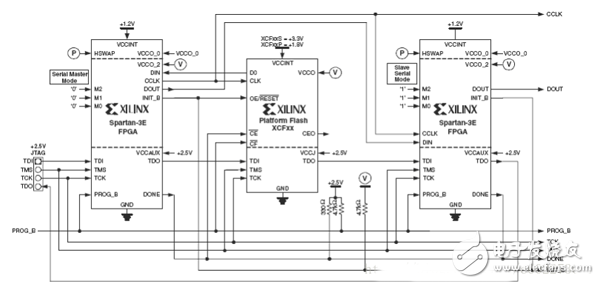

FPGA共有四种配置模式:从串模式(Slave Serial),主串模式(Master Serial),从并模式(Slave Parallel/SelectMap)以及边界扫描模式(Boundary-Scan)。具体的配置模式由模式选择引脚M2﹑M1﹑M0决定。不同的配置模式所对应的M2﹑M1﹑M0,配置时钟的方向以及相应的数据位宽。

主串模式——最常用的FPGA配置模式。

在主串模式下,由 FPGA 的 CCLK 管脚给 PROM 提供工作时钟,相应的 PROM 在 CCLK 的上升沿将数据。从 D0 管脚送到 FPGA 的 DIN 管脚。无论 PROM 芯片类型 ( 即使其支持并行配置 ),都只利用其串行配置功能。

主串配置电路最关键的 3 点就是 JTAG 链的完整性、电源电压的设置以及 CCLK 信号的考虑。

多片FPGA通信:

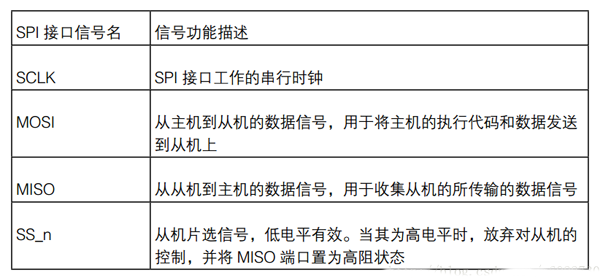

SPI串行Flash配置模式:

串行 Flash 的特点是占用管脚比较少,作为系统的数据存贮非常合适,一般都是采用串行外设接口 (SPI 总线接口 )。

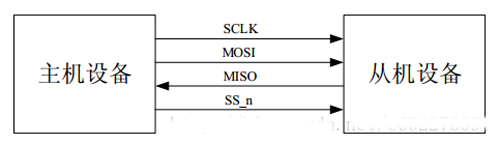

FPGA 通过 SCLK 控制双方通信的时序,在 SS_n 为低时,FPGA 通过 MOSI 信号线将数据传送到 FLASH,在同一个时钟周期中,FLASH 通过 SOMI 将数据传输到FPGA 芯片。无论主、从设备,数据都是在时钟电平跳转时输出,并在下一个相反的电平跳转沿,送入另外一个芯片。

本文导航

- 第 1 页:FPGA开发配置模式电路设计精华集锦

- 第 2 页:在串行模式电路设计

- 第 3 页:JTAG配置模式电路设计