您现在的位置是:首页 > 电路图 > 电机控制电路 > 电机控制电路

卫星高速基带传输的抗同步开关噪声设计

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

简介关键词:同步开关噪声基带传输噪声电路板 俞凌筠,韩佳鑫,孙立达 (上海卫星工程研究所, 上海 200240) 摘要:对高速基带传输中产生噪声" title="同步开关噪声" target="_blank"同步开关噪

关键词: 同步开关噪声 基带传输 噪声 电路板

俞凌筠,韩佳鑫,孙立达

(上海卫星工程研究所, 上海 200240)

摘要:对高速基带传输中产生噪声" title="同步开关噪声" target="_blank">同步开关噪声的原因进行了深入分析。通过理论分析和试验数据,提出了抗同步开关噪声的方法。对于今后在高速基带设计中避免同步开关噪声有一定的指导意义。

关键词: 同步开关噪声;基带传输

0引言

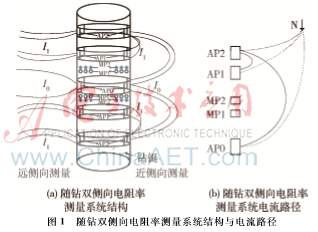

图1高速基带传输设计原理图随着卫星基带设备电路板上大量使用高集成度的高速数字芯片,同步开关噪声(Simultaneous Switching Noise,SSN)问题成为制约高速基带传输设计的一个瓶颈。同步开关噪声是指当器件上多个逻辑电路或I/O管脚同时处于开关状态时,产生瞬间变化的电流,在经过回流路径上存在的电感时,形成交流压降,从而引起噪声。如果引起地平面的波动,就会造成芯片地与系统地不一致,这种现象称为地弹[12]。

同步开关噪声的危害是非常大的,会增加电源噪声,影响信号的质量和时序,产生毛刺,从而导致数字电路误采样[3]。另外,同步开关噪声引起的问题一般隐藏得很深,只有在器件多个逻辑单元同时开关时才会发生,用正常的业务测试方法很难发现,容易漏测[4]。针对高速基带传输中的同步开关噪声问题,本文提出了优化设计方案。

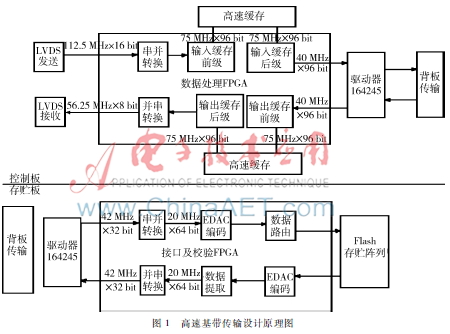

1高速基带传输设计

某卫星型号高速基带传输设计如下:数据处理FPGA通过LVDS接口接收外部112.5 Mb/s×16 bit高速数据流,对其进行串并转换后缓存,利用驱动器164245建立96 bit并行数据传输,通过背板传输至接口及校验FPGA进行后续数据处理,其中背板上单位传输速率为40 Mb/s。其设计原理图如图1所示。

在上述传输条件下,当传输随机数据序列时,传输结果无误码;而在传输含有长0或长1的数据序列时,产生了大量的误码。通过对背板传输信号进行监视,发现在传输长0或长1数据时,产生了同步开关噪声。本该传输0的某些时间点出现了毛刺,该毛刺信号接近接收器的门限,从而导致误判。

2同步开关噪声产生原因分析

2.1开关驱动器数量

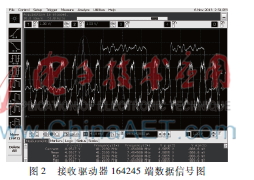

开关驱动器的数量为在并行传输中逻辑0向逻辑1跳变的位数数量。开关驱动器的数量由并行传输的总位数和数据源的类型两方面决定。近年来由于卫星载荷高速传输的需求,使得背板基带传输中传输位数由32 bit增加到96 bit,且载荷数据随机性不强,常常含有长0长1的数据。因此,并行传输的位数增加和传输含有长0长1的数据序列增加了开关驱动器的数量,当开关驱动器增加到一定数量时,就会引发同步开关噪声,产生毛刺,造成误判,如图2所示。

2.2回路电感

电路板级的电源必须通过感性连接器为元器件提供各种瞬时的电流需求。在电路板级任何流经连接器的电流必须有对应的供电电源,并通过电源引脚和接地引脚返回。由于电流在连接器上必须通过接地引脚返回电源,当接地引脚与目标信号引脚之间的距离增加时,总的回路电感将增大。如果回路不连续,且若干个输出对应的返回电流流经一块很小的区域,则同步开关噪声会急剧增大。

图3背板引脚分配示意图根据背板的引脚分配图(如图3所示),通过对引脚A31和A24上的眼图信号进行分析(A31引脚离电源地最近,A24引脚离电源地最远),发现离电源地近的引脚A31的信号眼图质量比离电源地远的引脚A24的好,如图4、图5所示。因此,引脚离电源地越远,回路电感越大,同步开关噪声越大;反之,同步开关噪声越小。

2.3开关时间

开关同步时间为驱动器上由0跳变至1或由1跳变至0的时间。板级上的走线本身有着一定的寄生电容,通过串接电阻即可实现RC充放电电路,调节电阻的阻值即可改变充放电时间。通过对上节同步开关噪声最严重的引脚24进行不同阻值的电阻(33 Ω、51 Ω)串接后再对其眼图进行监测,发现串接51 Ω电阻后的信号眼图质量比串接33 Ω的好,如图6、图7所示。因此,串联电阻的阻 图7引脚24串接51Ω电阻眼图值越小(或不串接电阻),开关时间越短,同步开关噪声越大;反之,同步开关噪声越小。

3高速基带传输抗同步开关噪声设计

针对多位并行高速传输容易造成同步开关噪声的缺点,抗同步开关噪声设计的方案包括对数据源传输前后进行加解扰处理、增加接地引脚数量并合理分配其位置、在背板传输线上串联电阻三个方面。

由于高速基带传输无法降低并行传输位数,因此只能通过增加传输数据的随机性来减小开关驱动器的数量,从而有效地抑制同步开关噪声。通过在数据源传输前对数据源进行加扰,传输后进行解扰的方法增加传输过程中数据源的随机性,从而有效减小传输过程中同步开关驱动器的数量。

在PCB板设计时增加接地引脚数量,合理分配接地引脚的位置,保证每个传输节点附近都分布接地引脚,使得板级电流回路畅通,从而减少回路电感,减小同步开关噪声。

在背板每位传输线中串接电阻,增加驱动开关时间。考虑串联电阻与输出阻抗的匹配性,选择串接51 Ω的电阻。

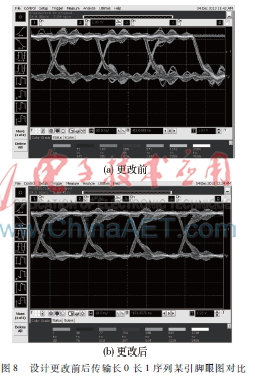

按照上述优化方案,对某型号卫星高速基带传输设计进行优化更改,对优化后的设计采用长0长1数据样本进行测试,更改前后的某引脚眼图如图8所示,同步开关噪图8设计更改前后传输长0长1序列某引脚眼图对比声影响改善显著(毛刺现象减少)。误码率测试中,测试样本数据量大于1 GB,测试结果显示测试误码率为0。

4结束语

本文结合卫星高速基带传输设计的工程实际,对同步开关噪声产生的原因进行了分析,并进行了设计改进。通过对多种数据样本的测试,验证了改进设计的有效性,对今后高速基带传输的设计具有一定的指导意义。

参考文献

[1] 张颖.高速PCB电路中同步开关噪声抑制方法研究[D].西安:西安电子科技大学,2012.

[2] 宋万均,张安堂.双基地雷达目标速度计算的FPGA实现[J].电子技术应用,2014,40(1):4749,52.

[3] 张从力,史记征.扩频技术在矿井透地通信系统中的应用与仿真[J].微型机与应用, 2013,32(1): 5153,56.

[4] 陆增援. FPGA上同步开关噪声的分析[EB/OL].(20090403)[20160115].电子工程专