您现在的位置是:首页 > 电路图 > 电机控制电路 > 电机控制电路

浅析IC测试开发流程及量产数据对产品设计的影响

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

简介伍凤娟1,王媛媛2 (西安科技大学 电气与控制工程学院,陕西 西安 710054) 摘要:集成电路行业作为信息产业的基础,其应用领域上至国防军工下至家用电器。测试技术是检测集成电路

伍凤娟1,王媛媛2

(西安科技大学 电气与控制工程学院,陕西 西安 710054)

摘要:集成电路行业作为信息产业的基础,其应用领域上至国防军工下至家用电器。测试技术是检测集成电路质量好坏的重要环节,对集成电路进行测试可有效提高芯片的成品率。测试的主要目的是保证芯片在恶劣环境下能完全实现设计规格书所规定的功能及性能指标。主要论述半导体后道测试对产品工艺的影响,旨在降低测试成本,提高测试质量及测试精度。

关键词:半导体;集成电路测试;量产数据;产品工艺

中图分类号:TN407文献标识码:ADOI: 10.19358/j.issn.1674 7720.2016.20.008

引用格式:伍凤娟,王媛媛. 浅析IC测试开发流程及量产数据对产品设计的影响[J].微型机与应用,2016,35(20):31 33.

0引言

近年来,我国集成电路产业已成为半导体行业所关注的焦点。其中集成电路测试作为设计、制造和封装的有力技术支撑起着举足轻重的作用。集成电路测试水平的高低直接决定着集成电路性能、质量的好坏,因此受到业界的高度重视[1]。在集成电路领域,几乎所有的芯片在出货之前都要经过几道严格的测试,包括CP测试、FT测试及QA测试。每一道测试都会产生一系列的测试数据,由于测试程序通常是由一系列测试项目组成的,从各个方面对芯片进行充分检测,不仅可以判断芯片性能是否符合标准,是否可以进入市场,而且能够从测试结果的详细数据中充分、定量地反映出每颗芯片从结构、功能到电气特性的各种指标。

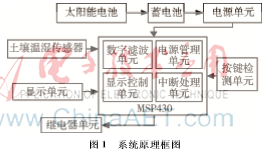

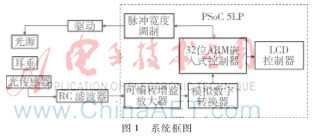

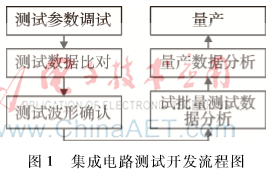

1集成电路测试开发流程

集成电路测试主要分为两大类:参数测试和功能测试。根据集成电路设计和制造过程中对测试的需求,可分为设计验证测试、晶圆测试、封装测试、可靠性测试[2]。针对不同类型的芯片,需要测试的具体项目会有所不同。如:运算放大器类产品通常需要测试静态电流ICC、失调电压VIO、失调电流IB、电压增益GV、电源抑制比PSRR、共模抑制比CMRR等;电源管理类产品需要测试基准电压Vref、工作频率Fosc、启动电压Vst、关断电压Vuvlo等。这些测试项是产品电气特性的直接体现,更是产品质量的灵魂[3]。集成电路测试开发就是针对这些测试项进行准确、快速、稳定的测试。具体开发流程如图1所示。

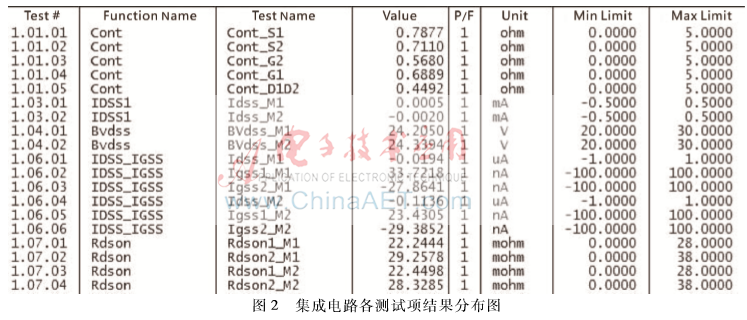

(1)测试参数调试

利用集成电路专用的测试系统开发平台,按照产品设计指标及产品设计要求完成对待测芯片各测试项的调试,直至所有测试结果均分布在产品特性的Limit区间内。集成电路各测试项的测试结果分布情况如图2所示。

(2)测试数据比对

取一定数量的待测芯片,将经过测试参数调试后所得的测试数据与样品数据作差值比对,若差值在容许范围内则测试系统给出的测试结果为Pass,否则为Fail。测试数据与样品数据比对结果如图3所示。

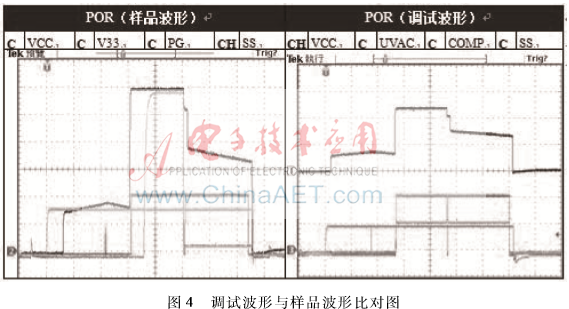

(3)测试波形确认

为了确保测试程序正确可靠,需要对波形进行确认。通常情况下取一颗芯片,针对具体测试项,将通过示波器观察到的调试波形与样品波形作比对,从而确保波形一致性。某芯片的调试波形与样品波形的比对图如图4所示。

以上三步做完之后,一个基本的测试程序开发流程就完成了。接下来分析量产测试数据对产品工艺的影响。

2集成电路量产测试数据对产品工艺的影响

集成电路工艺的不断演进及设计技术的不断提高,使集成电路测试技术面临双重挑战:制造工艺发展所带来的测试质量提高(包括新的故障类型、新的测试向量生成方法和可靠性保障等)和设计规模不断发展所带来的测试成本增加[4](包括不断延长的测试时间、不断增长的测试数据以及对新型测试设备的要求)。当芯片出货量巨大时,所有这些产品的测试数据整合在一起就能够在很大程度上反映出整个产品在设计和工艺制造上的一系列问题,而这些问题是难以在实验室通过对小批量产品进行分析所获得的。很多经验丰富的设计公司都非常重视对实际量产数据的追踪和分析,通过对这些测试数据的合理分析和利用,就能够找到该产品在设计和生产工艺上存在的各种问题,从而帮助设计人员和生产厂改善产品的性能和良率,甚至规避未来可能出现的产品设计质量隐患。然而,遗憾的是国内很多设计公司往往忽略了这一点,或者即使意识到了量产测试数据的重要性,却也不知道从哪里入手、怎样去分析这些数据。因此,如何分析利用这些数据非常重要。

2.1量产数据与产品良率的关系

首先需要纠正的一个误区是:很多设计公司在追踪产品测试数据时只关心产品最终的良率,这显然是不够的。产品的某些突发工艺问题并不一定直接反映在产品最终良率变化上,所以在观察产品良率的同时必须追踪各个fail bin的比例变化。当某个fail bin的比例突发或渐进地发生明显变化的时候,就需要设计人员对其进行深入调查,因为这很可能是导致产品品质波动的一个重要因素。

其次,测试程序的所有项目中除了纯数字电路的测试只返回Pass/Fail信息外,其他项目结果往往都含有具体的测试数值,这些数据都反映了一颗芯片自身的某些特性,所以也必须加以恰当地计算和分析。比较常用的方法除了计算每批产品的各个测试数值的平均值外,还需要通过计算正态分布的标准方差来获得Cp/Cpk值。只有当这些统计结果和历史数据都基本吻合时,才可以大致认为该产品的品质是可接受和可控的。实验证明,为保证产品良率,应尽量使Cp>3.3、Cpk>1.3,否则很可能会导致良率低下或不稳定造成的各种损失。

最后,通常会被严重忽略却又至关重要的一项指标是结果一致性确认。很多产品由于出货量巨大,往往需要多台测试机同时进行测试,每台测试机有多个测试工位[5]。由于硬件有可能发生各种异常甚至事故,影响测试结果,因此测试人员必须随时确认各台测试机以及测试工位之间的测试结果是否一致[6]。通常情况下,某台设备的某个工位发生问题导致良率下降往往会被总体良率数据所“淹没”。若测试人员只关注总体良率的变化而不注重硬件之间的结果一致性指标,这些问题就会被忽略,从而导致经济上的一系列损失。

2.2Wafer级别CP测试数据分析

与基于分离芯片的FT测试最大的不同是:CP测试是以Wafer为基本单位的,其测试结果数据不仅仅是每个die的测试结果,还包含了各个数据在整个Wafer甚至整个Lot内的分布信息[7]。这些信息是和硅片加工的工艺条件紧密结合的,能够给设计人员和工艺工程师提供大量的量产信息,这是FT测试结果所望尘莫及的。

最典型的一个CP数据分析方法是对Wafer面内测试结果分布倾向的统计。由于单枚Wafer的面内测试结果分布受随机因素影响较大,因此将多枚Wafer的数据根据MAP图叠加在一起进行统计和计算[8]。图5所示为某款芯片的CP测试良率面内分布示意图。由图可明显看出该Wafer中间良率和周边良率的不同,通过此信息可反推生产工艺上存在的问题,然而这些重要现象仅靠观察每片Wafer的整体良率是无法及时发现的。

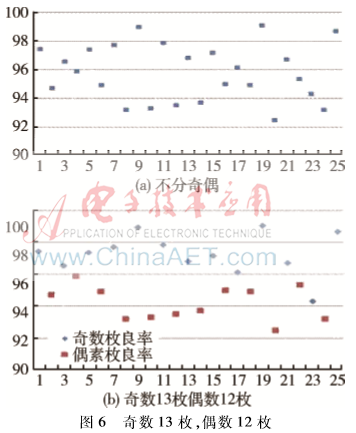

此外,还要确认Wafer之间以及Lot之间测试数据的变化。该指标可直接反映出Wafer之间的生产工艺稳定性,若Fab厂的生产工艺不稳定或发生过突发事故,就很容易从这个指标看出问题所在。图6为Lot内25枚Wafer的良率分布图。

图6(a)中,除了良率波动较大以外,很难看出其他的相关信息,而从图6(b)中就很容易发现Wafer的良率在单数枚和偶数枚上的明显差距:单数13枚Wafer的平均良率为97.29%,而偶数12枚Wafer的良率只有94.16%。如果产品工程师对Fab工艺有足够了解,就可以从数据上推测,良率问题很可能和生产线上某台双腔设备故障有关。因为如果设备有两个腔对Wafer进行单枚轮流作业(比如一些干刻和CVD设备),必然是单数枚Wafer在一个腔加工而双数枚在另一个腔加工,一旦某个腔内工艺条件出现问题,就会发生上述良率分布异常的现象。可见, Wafer间良率变化对产品工艺影响很大。

3结论

在集成电路测试开发初期,要根据测试流程严格比对确认,确保测试开发的可靠性、精度及稳定性。只有在前期进行足够的验证工作,才能在正式量产中做到高质量、低成本。同时,作为信息宝库重要数据的量产测试数据往往被很多设计公司所忽视,因此要高度重视对量产测试数据的分析,及时预判可能出现的异常信息并做出改进,从而提高产品工艺及质量。

参考文献

[1] 俞建峰,陈翔,杨雪瑛.我国集成电路测试技术现状及发展策略[J].中国测试,2009,35(3):1-5.

[2] 刘新福,杜占平,李为民. 半导体测试技术原理与应用[M].北京:冶金工业出版社,2007.

[3] 夏开峰. 数据挖掘技术在半导体测试管理系统中的应用[J].信息与电脑,2010(12):147.

[4] 汪天伟. 混合集成电路测试硬件电路测试板的设计[D].成都:电子科技大学,2013.

[5] MORAVEK O, HOFFMAN K.Measurement and simulation of Coaxial to Microstrip ransitions radiation properties and substrate influence[J].Radio Engineering,2012,2(25):568-572.

[6] JJG(军工)32 2014.模拟集成电路测试系统检定规程[S].北京:国家国防科技工业局,2014-05-20.

[7] 秦国林,许斌,罗俊.集成电路圆片级可靠性测试[J].微电子学,2013,20(1):144-145.

[8] 王晔.SoC芯片并行测试中几个值得关注的问题[J].半导体技术,2010,35(12):1199-1203.