您现在的位置是:首页 > 电气技术 > 电气技术

时序逻辑电路中的计数器

![]() 来源:艾特贸易2018-08-13

来源:艾特贸易2018-08-13

简介计数器是一种累计并寄存输入脉冲数目的时序逻辑电路。它在计算机、自动控制装置中被广泛用于计数、定时、分频及逻辑控制等方面。 计数器的种类繁多,按进位制来分有二进制计数

计数器是一种累计并寄存输入脉冲数目的时序逻辑电路。它在计算机、自动控制装置中被广泛用于计数、定时、分频及逻辑控制等方面。

计数器的种类繁多,按进位制来分有二进制计数器和非二进制计数器,按计数增减而分有加法计数器和减法计数器,按计数器中各触发器状态翻转是否与触发信号同步分有同步计数器和异步计数器等。二进制计数器是各种类型计数器的基础。

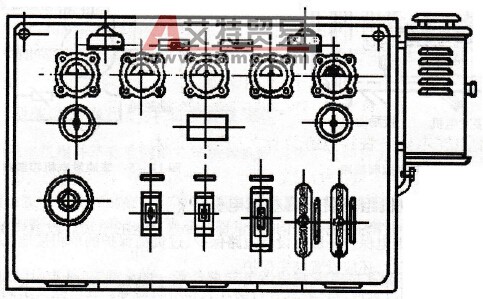

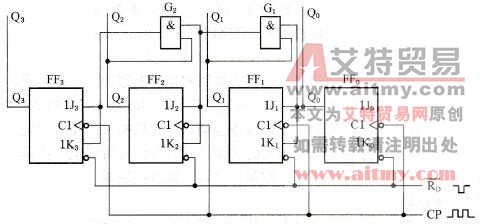

图9-24所示是用JK触发器和二输入端与门G1、G2组成的四位同步加法计数器。由图可知,计数脉冲是同时加到各触发器的输入C1端,因此各触发器状态变化几乎与计数脉冲同步,从而加快了计数速度。

图9-24 四位同步二进制加法计数器

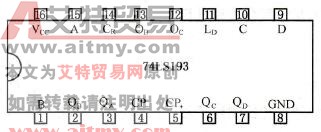

实用的同步二进制计数器已广泛采用现成的中规模集成计数器,如SN74193型同步计数集成电路就是一种具有预置数码、加减可逆计数的同步四位二进制可逆集成计数器,图9-25所示为其外引线排列图。图中A、B、C、D为数据输入端(A为最低位、D为最高位);QA、QB、QC、QD是数码输出端(QA为最低位、QD为最高位);OB为借位输出端(做减法计数时用),OC为进位输出端(做加法计数时用);CP+、CP-分别为加法与减法计数脉冲输入端;CR为置0端,LD为置数控制端。

图9-25 SN74193同步四位二进制可逆计数器外引线排列

当CP =1时,计数器置零。

当CP =0时,计数器输出状态与LD、CP+及CP-有关:①当LD =0时,QA、QB、QC、QD由输入数据A、B、C、D直接控制,达到预置数码之目的;②当LD =1时,若计数脉冲从CP+端输入则进行加法计数;若计数脉冲从CP-端输入则进行减法计数。

(作者稿费要求:需要高清无水印文章的读者3元每篇,请联系客服,谢谢!在线客服: )

)

点击排行

室内风扇电机和霍尔元件的检测

室内风扇电机和霍尔元件的检测