您现在的位置是:首页 > 电气技术 > 电气技术

时序逻辑电路中的数码寄存器

![]() 来源:艾特贸易2018-08-13

来源:艾特贸易2018-08-13

简介存放数码的组件称为数码寄存器,图 9-21 是由四个 D 触发器构成的四位数码寄存器的逻辑图。四个触发器的时钟脉冲输入端连在一起,它们受时钟脉冲的同步控制, D0 ~ D3 是寄存器并

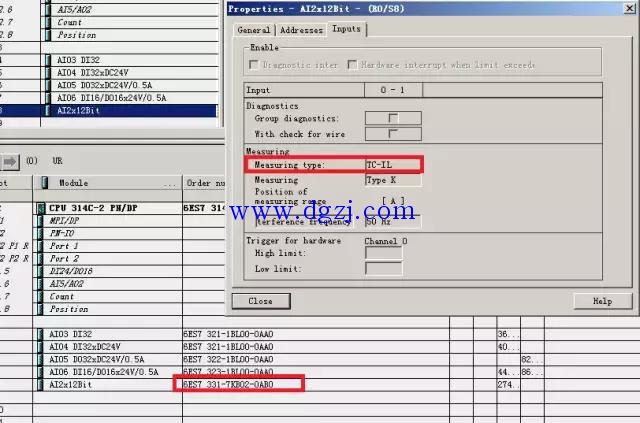

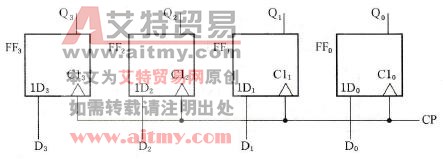

存放数码的组件称为数码寄存器,图9-21是由四个D触发器构成的四位数码寄存器的逻辑图。四个触发器的时钟脉冲输入端连在一起,它们受时钟脉冲的同步控制,D0~D3是寄存器并行的数据输入端,输入四位二进制数码,Q0~Q3是寄存器并行的输出端,输出四位二进制数码。

若要将四位二进制数数码为D0D1D2D3=1101存入寄存器中,只要在时钟脉冲CP输入端加时钟脉冲。当CP上升沿出现时,四个触发器的输出端Q0Q1Q2Q3=D0D1D2D3=1101,即四位二进制数码便同时存入四个触发器中,当外部电路需要这组数据时,可从Q0Q1Q2Q3端读出。

常用的数码寄存器有4位、8位等多种类型,如T451、T3175是4位寄存器,T4373是8位寄存器。

图9-21 四位数码寄存器

(作者稿费要求:需要高清无水印文章的读者3元每篇,请联系客服,谢谢!在线客服: )

)

点击排行

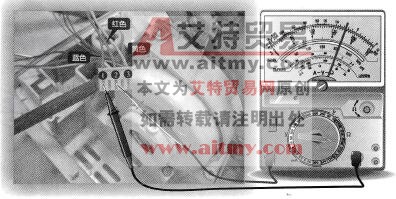

室内风扇电机和霍尔元件的检测

室内风扇电机和霍尔元件的检测