您现在的位置是:首页 > 变频技术 > 变频技术

降低高压MOSFET导通电阻的原理与技术方法

![]() 来源:艾特贸易2018-06-08

来源:艾特贸易2018-06-08

简介(1) 不同耐压的 MOSFET 的导通电阻分布。不同耐压的 MOSFET ,其导通电阻中各部分电阻比例分布也不同。如耐压 30V 的 MOSFET ,其外延层电阻仅为总导通电阻的 29% ,耐压 600V 的 MOSFET 的外延

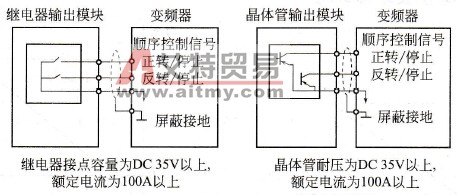

(1)不同耐压的MOSFET的导通电阻分布。不同耐压的MOSFET,其导通电阻中各部分电阻比例分布也不同。如耐压30V的MOSFET,其外延层电阻仅为总导通电阻的29%,耐压600V的MOSFET的外延层电阻则是总导通电阻的96.5%。由此可以推断耐压800V的MOSFET的导通电阻将几乎被外延层电阻占据。欲获得高阻断电压,就必须采用高电阻率的外延层,并增厚。这就是常规高压MOSFET结构所导致的高导通电阻的根本原因。

(2)降低高压MOSFET导通电阻的思路。增加管芯面积虽能降低导通电阻,但成本的提高所付出的代价是商业品所不允许的。引入少数载流子导电虽能降低导通压降,但付出的代价是开关速度的降低并出现拖尾电流,开关损耗增加,失去了MOSFET高速的优点。

以上两种办法不能降低高压MOSFET的导通电阻,所剩的思路就是如何将阻断高电压的低掺杂、高电阻率区域和导电通道的高掺杂、低电阻率分开解决。如除导通时低掺杂的高耐压外延层对导通电阻只能起增大作用外并无其他用途。这样,是否可以将导电通道以高掺杂较低电阻率实现,而在MOSFET关断时,设法使这个通道以某种方式夹断,使整个器件耐压仅取决于低掺杂的N-外延层。基于这种思想,1988年INFINEON推出内建横向电场耐压为600V的COOLMOS,使这一想法得以实现。内建横向电场的高压MOSFET的剖面结构及高阻断电压低导通电阻的示意图如图1-5所示。

与常规MOSFET结构不同,内建横向电场的MOSFET嵌入垂直P区将垂直导电区域的N区夹在中间,使MOSFET关断时,垂直的P与N之间建立横向电场,并且垂直导电区域的N掺杂浓度高于其外延区N-的掺杂浓度。

当UGS<UTH时,由于被电场反型而产生的N型导电沟道不能形成,并且D、S间加正电压,使MOSFET内部PN结反偏形成耗尽层,并将垂直导电的N区耗尽。这个耗尽层具有纵向高阻断电压,如图1-5 (b)所示,这时器件的耐压取决于P与N-的耐压。因此N-的低掺杂、高电阻率是必须的。

图1-5 内建横向电场的MOSFET剖面,垂直N区被夹断和导通

(a)内建横向电场的高压MOSFET断面结构;(b)垂直的N区被耗尽;(c)导电沟道

形成后来自源极的电子将垂直的N区中正电荷中和并恢复N型特征

当UGS>UTH时,被电场反型而产生的N型导电沟道形成。源极区的电子通过导电沟道进入被耗尽的垂直的N区中和正电荷,从而恢复被耗尽的N型特性,因此导电沟道形成。由于垂直N区具有较低的电阻率,因而导通电阻较常规MOSFET将明显降低。

通过以上分析可以看到:阻断电压与导通电阻分别在不同的功能区域。将阻断电压与导通电阻功能分开,解决了阻断电压与导通电阻的矛盾,同时也将阻断时的表面PN结转化为掩埋PN结,在相同的N-掺杂浓度时,阻断电压还可进一步提高。

(作者稿费要求:需要高清无水印文章的读者3元每篇,请联系客服,谢谢!在线客服: )

)