您现在的位置是:首页 > 电路图 > 电机控制电路 > 电机控制电路

近红外光信号采集的FPGA控制接口设计与实现

![]() 转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

转载来源:电子技术应用-AET chinaaet.com 电子发烧友 elecfans.com2017-03-23

简介谢宏,万兵,杨文璐,夏斌,姚楠 (上海海事大学 信息工程学院 上海 201306) 摘要:介绍了一种近红外信号采集模块的设计方案,它主要采用ADS1299采样芯片,利用FPGA的可编程逻辑控制

谢宏,万兵,杨文璐,夏斌,姚楠

(上海海事大学 信息工程学院 上海 201306)

摘要:介绍了一种近红外信号采集模块的设计方案,它主要采用ADS1299采样芯片,利用FPGA的可编程逻辑控制的特点,采用状态机编程思想,通过编程设计A/D的读控制时序和写控制时序,将采样结果实时保存在双口RAM里,并通过NiosII软核处理器进行控制,从而实现高精度多通道A/D采样系统采集模块的设计。通过实验表明,该设计是有效可行的。

关键词:近红外信号;FPGA;NIOSII;ADS1299;A/D采集模块;状态机

0引言

21世纪是生物科学与脑科学的时代,功能近红外光谱技术(Functional NearInfrared Spectroscopy, FNIRS)是一种新兴的脑功能检测技术,它利用近红外光波段700-900 nm在大脑中传播的吸收特性,能够提供基于血红蛋白浓度变化的血液动力学信息,反映大脑皮质的血氧代谢状况,可用于脑功能活动的检测。相比于传统脑电信号(EEG)的检测方法,它具有高的时间分辨率、实时性、抗干扰性以及高稳定性等优点[1]。

目前的脑功能信号采集设备的体积往往较大,只能用于固定场所,不便于实时信号获取,不能用于突发状况,因此急需一种便捷式脑功能信号采集设备。在便捷式脑功能信号采集方面,国外研究较早,技术比较成熟,已做出产品,但售价昂贵。国内方面大多处于数据处理、特征提取和应用研究上,对相关仪器的研发偏少,更没能开发出相关的系统[2],因此研究便捷式脑功能信号采集的设备具有重要的意义。

为了完整反映脑部的不同区域活动情况,需要同时采集多路数据,因此对信号处理的实时性、抗干扰性与精度有很高的要求,而ADS1299的8路低噪声24位同时采样的特性能很好地满足了这一需求。它是一款常用脑电信号的采集芯片,由于近红外信号比脑电信号稳定得多且受到的干扰较小,因此同样也适合近红外信号的采集,在同等条件下,采集的数据更加准确可靠,而且高度集成,其体积小、功耗低等优点对便捷式系统的设计十分的有利[3]。在主控芯片的选取中,很多文献都是采用单片机、ARM以及DSP作为主控制芯片,如文献[4]、[5]等,使其在运行速度、数据处理、接口灵活性以及对功能的扩展方面都有各自的局限性,往往顾此失彼,不能兼得,而FPGA强大的功能不但综合了它们的优点,而且克服了这些不足,十分适合作为主控芯片。因此,本文提出了一种基于ADC+FPGA+PC架构的方案,设计一个高度集成的便捷式近红外光信号采集系统。

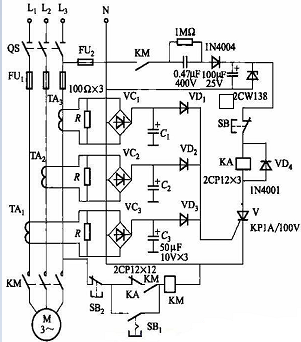

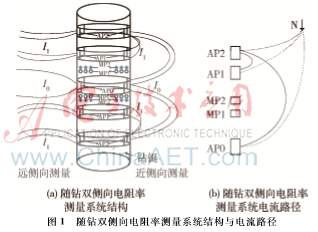

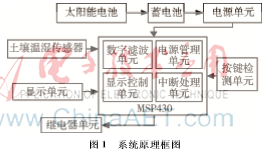

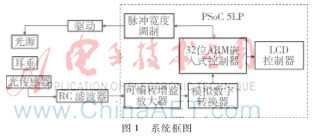

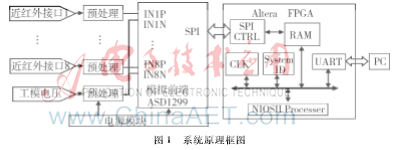

1总体设计

基于功能近红外光谱技术的原理,将近红外LED的760 nm、850 nm波长的发射光强分别调制在0.8 KHz和1.2 KHz的正弦波上,实现了两个波长的频分复用,而在不同通道之间,采用时分复用进行传输,从而实现近红外信号的多路传输。此后,发射出的近红外信号经过大脑反射后通过光电转换芯片转换为电信号,再经过预处理(阻抗匹配和低通滤波)后,进入集成模拟前端。根据采集的信号频率和奈奎斯特采样定理,TI公司的A/D转换芯片ADS1299的250~16 kS/s的采样速度能够很好地满足要求,24位的极高采样精度也大大降低了对信号预处理的要求,且信号稳定,无需采用差分输入方式。系统采用Altera公司的FPGA芯片EP2C20F484C7作为主控芯片,利用硬件描述语言(VHDL)将GPIO口配置成通用串行SPI口,用SPI与ADS1299进行通信。在FPGA内部配置了一个双口的RAM,用于实时存储ADS1299的输出结果。FPGA内部采用Avalon_MM总线进行通信,CPU采用NIOSII软核处理器,处理后的数据通过UART总线传输至PC。其系统原理框图如图1所示。

2FPGA控制ADS1299的实现

2.1ADC与FPGA接口模块设计

2.1.1SPI接口控制原理

串行外围设备接口(Serial Peripheral Interface,SPI)是一种高速、全双工、同步的通信总线。它仅需四条信号线,不仅仅节约了管脚,而且对PCB的布局十分有利。正是由于这种简单易用的特性,许多公司的芯片都集成了这种通信协议。而ADS1299正是采用了这种协议[6]。

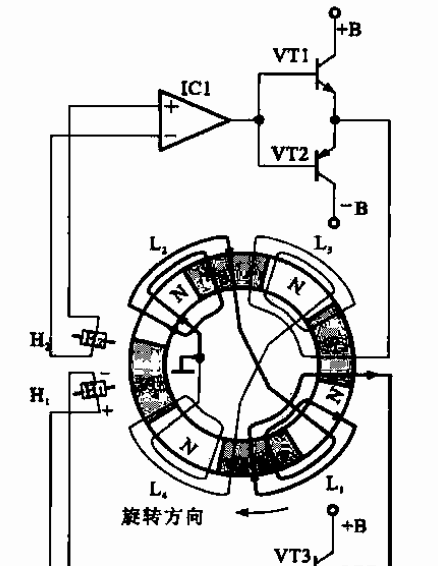

ADS1299的SPI接口由四条信号线组成,分别定义为CS、SCLK、DIN和DOUT。其中CS是芯片的片选信号,只有CS有效时(一般为低电平有效),对芯片的操作才可行有效,根据CS这一特性,可以在同一总线上连接多个SPI设备,而使其数据的传输不产生冲突。SCLK是SPI同步时钟信号,该信号多由主机产生,数据信号往往在该时钟的上升沿或下降沿逐位进行传输。DIN和DOUT是主从机进行通信的数据信号,DIN即主机的输入或者说是从机的输出,DOUT即主机的输出或者说是从机的输入。SPI的工作模式有两种:主模式和从模式。SPI总线可以配置成单主单从、单主多从和互为主从三种通信方式。在设计中,将FPGA作为SPI的主机,ADS1299作为从机,使其处于单主单从的工作模式。其中的信号CS和SCLK是由FPGA内部信号控制产生的。

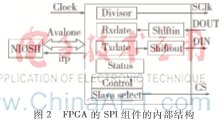

图2是FPGA的SPI组件的内部结构。SPI组件通过Avalone总线和中断请求信号irq与NIOSII处理器相连。内部也有一个divisor寄存器,也是对其输入工作时钟进行分频得到最终与外设接口的时钟sclk。rxdata和txdata寄存器用于NIOSII处理器读写收发数据,与它们直接接口的还有一个串并转换的移位寄存器shifin和一个并串转换的移位寄存器shifout。NIOSII可以从status寄存器读取当前SPI组件的状态,slave select寄存器主要是在拥有多个从机时控制其片选。

2.1.2有限状态机编程思想与时序程序设计

有限状态机是一类很重要的时序电路,是许多数字电路的核心部分,且有限状态机的编程设计具有高速性、可靠性、稳定性的特点。因此,对于ADC与FPGA接口模块与双口RAM读写模块,将采取有限状态机进行编程。与传统的用CPU按照指令逐条运行的操作方式相比,采用状态机的形式,可以在每个状态中并行同步完成许多运算和控制操作,而且一般用状态机构成的硬件系统比对应的用CPU按照指令完成同样功能的系统的工作速度要高出3~5个数量级,是其高速性的具体体现。在可靠性与稳定性方面,由于其运行不依赖软件指令逐条执行,且是由FPGA中的纯硬件电路构成,因此不存在CPU运行软件过程中的许多缺陷,具有很高的可靠性与稳定性[7]。

图3是ADS1299串行接口的状态转换图。将其划为24个有限状态,S_Idle 为空闲状态,S_CS、S_Wreg_1、S_Wreg_2、S_ID、S_config1、S_config2、S_config3、S_Loff、S_CH1_set、S_CH2_set、S_CH3_set、S_CH4_set、S_CH5_set、S_CH6_set、S_CH7_set、S_CH8_set、S_Bias_sensp、S_Bias_sen、S_Loff_sensp、S_Loff_sensn、S_Loff_fli、S_Loff_statp、S_Loff_statn、S_Gpio、S_Misc1、Misc2、S_config4为ADC内部寄存器配置的初始状态。S_Start_c为指令控制ADC起始的转换状态(ADC由指令进行控制,此时芯片上START引脚接低电平)。S_Start为ADC数据转换状态,控制ADC的数据转换。S_DRDY是数据已经转换好,可以输出的使能状态,低电平有效,在输出时钟的第一个上升沿时拉高。S_CS_Assert为片选状态。S_RDATA控制其进入单口传输模式进行数据传输(ADC内部数据传输有两种模式:持续传输模式与单口传输模式,其中单口传输模式更适合脑电信号的传输)。S_STAT、S_CH1、S_CH2、S_CH3、S_CH4、S_CH5、S_CH6,S_CH7、S_CH8为ADC内部状态寄存器与八通道的数据输出状态。S_Stop_c为控制转换的停止状态,此时ADC停止工作。

2.2双口RAM的读写

所谓的双口RAM就是在一个SRAM存储器上具有两套完全独立的数据线、地址线和读写控制线,其最大的特点是存储数据共享,并允许两个独立的CPU或控制器同时对该存储器进行随机性的读写访问,即可以同时异步地对存储器进行读写[8]。基于以上特点,可以将采样结果实时储存在双口RAM里,处理器可实时读取采样结果,这样能够不占用处理器资源,大大提高了处理器的工作效率[9]。图4是简单的双口RAM的接口配置电路。

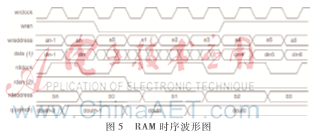

根据双口RAM的工作原理和读写时序要求。其时序波形图如图5所示。

2.3结果分析

整个设计是在Altera公司提供的Quartus II、NIOS II Software Build Tools for Eclipse以及Modelsim等软件平台上完成的,整体采用VHDL硬件语言设计,FPGA通过Avalon_mm总线与各模块进行通信,外部通过UART与PC之间进行数据交互。

通过Modelsim仿真测试,测得用状态机编写ADS1299与FPGA接口的部分仿真时序如图6所示。

双口RAM的读写时序如图7所示。

3结论

本文设计的基于FPGA 控制、双口RAM存储的高速数据采集系统具有可靠性高、数据不丢失、抗干扰性强、便于数据传输、存储、显示和处理及可扩展性好等优点。其相比于传统采集系统设计,一方面,简化了硬件电路;另一方面,减少了对处理器资源的占用,对提高处理器的效率具有很大意义。实验表明,系统的各项指标均达到要求,具有很强的工程实用价值。

参考文献

[1] 张岩.基于近红外光谱技术的脑功能活动信号提取方法研究[D].哈尔滨:哈尔滨工业大学, 2011.

[2] 谢宏,王光明,姚楠,等.可穿戴式的功能近红外光谱成像系统的前端设计[J].微型机与应用,2015,34(10):29 31.

[3] TI.ADS1299EEG FE user’s guide[OL].(2012 01 XX)[2016 03 28]http://focus.ti.com.cn/cn/lit/ds/syml ink/slau443.pdf.

[4] 孙广金.基于ADS1299的新型脑电采集系统设计[J].机械与电子,2014(1):73 74.

[5] 宋勐翔,陈兰岚.基于ADS1298与STM32F407的心电采集与显示系统设计[J].现代电子技术,2015(13):141 144.

[6] 吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010.

[7] 王小进, 涂煜. 基于AD7606的继电保护数据处理设计[J].船电技术,2014,34(9):46 49.

[8] 谢宏,李亚男,夏斌,等.基于ADSl299的可穿戴式脑电信号采集系统前端设计[J].电子技术应用,2014,40(3):86 89.

[9] 唐永辉,徐鸣谦,乌建中.双口RAM在嵌入式多CPU系统中的应用[J].制冷空调与电力机械,2005(1):49 52.