您现在的位置是:首页 > PLC技术 > PLC技术

时间控制逻辑的PLC程序设计

![]() 来源:艾特贸易2017-06-04

来源:艾特贸易2017-06-04

简介一个控制系统中往往含有时间控制环节, PLC 控制系统中的时间控制环节通常是由 PLC 的内部时间控制单元来实现的。计时器是 PLC 中最常用的而且是最有效、最重要的时间控制单元。通

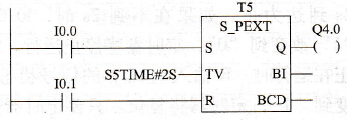

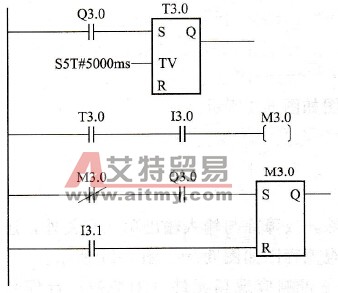

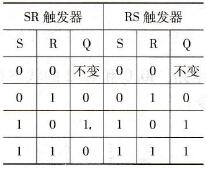

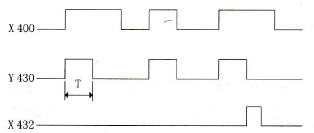

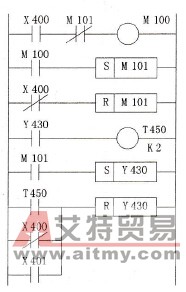

一个控制系统中往往含有时间控制环节,PLC控制系统中的时间控制环节通常是由PLC的内部时间控制单元来实现的。计时器是PLC中最常用的而且是最有效、最重要的时间控制单元。通过对计时器控制功能与其他逻辑指令的结合,可以实现许多工程中难以解决的时间控制问题。 有的PLC指令系统中已经给出了几种不同的时间控制功能指令,可以直接使用。而大部分指令系统只提供了一种最基本的计时单元,通过它与其他逻辑控制指令组合才能实现各种时间控制方式。常用时间控制逻辑包括: ·脉冲跟随逻辑; ·定宽脉冲逻辑; ·延时置位逻辑; ·记忆延时置位逻辑: ·延时复位逻辑等。 下面,以脉冲跟随逻辑的实现为例来说明时间控制逻辑程序的设计方法。 脉冲跟随逻辑中的输出信号随输入信号的变化而变化,但又受到设定时间的限制,信号状态如图5.9所示。 ·当输入信号X400由“0”变为“1”状态并保持时,输出Y430信号跟随输入信号X400, 并保持宽度为计时时间的脉冲宽度。 ·若X400的信号不保持足够时间,则输出Y430信号就只能跟随输入信号X400变为 “0”状态。 ·若复位信号出现时,输出Y430信号也变为“0”状态。 这种逻辑关系程序设计的关键问题是信号跟随的处理:即当输入信号由“0”变为“1”时,输出信号也由“0”变为“1”状态,当输入信号由“1”变为“0”时,输出信号也变为“0”状态。接下来的问题就是计时问题了。 根据以上分析,可得出输出信号的几种变化情况。 ·使输出信号置位的情况只有一种.即输入信号的上升沿。 ·使输出信号复位的情况有3种,计时时间到位信号、输入信号的下降沿、复位信号的 上升沿。 ·输出信号处于“1”状态时,若复位信号出现上升沿,则输出信号就被置位,直到下 一个输入信号出现上升沿。 实现脉冲跟随逻辑的梯形图如图5.10所示。 图5.9 脉冲跟随逻辑状态关系图

图5.9 脉冲跟随逻辑状态关系图 图5.10 脉冲跟随逻辑程序

图5.10 脉冲跟随逻辑程序

点击排行

PLC编程的基本规则

PLC编程的基本规则